面向AI数据中心高压中间母线赈济器应用的横向GaN HEMT、SiC MOSFET与SiC Cascode JFET的对比

节录

跟着AI数据中心向更高功率密度和更高效动力分派演进,高压中间母线赈济器(HV IBC)正渐渐成为下一代云贪图供电架构中的关键器件。本文针对横向GaN HEMT、碳化硅MOSFET及SiC Cascode JFET(CJFET)三类宽禁带功率器件,在近1 MHz高频开关要求下用于高压母线赈济器的性能张开对比分析。要点评估了导通损耗、开关特质、栅极电荷损耗及缓冲电路需求等关键方针。同期,本文亦探讨了三种谐振赈济器拓扑——堆叠式LLC、单相LLC与三相LLC——对其系统后果与元件数目的影响。仿真结果标明,尽管三类半导体器件的系统总损耗邻近,但CJFET因结构约略、驱动节略,在资本方面具备权臣上风。在拓扑比较中,三相LLC通过有用裁汰RMS电流并减少元件数目,发达出更优的概括性能。本连络为畴前高压IBC假想中半导体选型与拓扑建树提供了表面依据,安森好意思(onsemi)正开展有关践诺考据职责。

小序

现时,云贪图供电架构正朝着更高传输电压的标的演进。这一趋势不仅体面前数据中心与电网的勾通神态上——将通过固态变压器径直接入中压电网,也体面前数据中心里面的电力分家数统中——其正沉静转向高压直发配电架构。在该架构下,贪图托盘将径直勾通至800V直流母线,随后通过高压IBC将电压降至50V或12V,为下贱负载供电。

高压IBC具备以下关键特质:

• 杀青电压降压(16:1或64:1变换比)

• 提供电气断绝以保险安全

• 非稳压输出

• 具备短时过载才略

• 超紧凑的外形尺寸

• 赈济后果高

本白皮书将要点围绕杀青上述意见的赈济器拓扑结构与半导体技能张开探讨。本色主要聚焦于原边的拓扑采用与半导体器件;副边假设采用低压硅基MOSFET,并建树为中心抽头电流倍增器或全桥结构。

半导体技能

为温和高压IBC在袖珍化假想中无源元件的布局要求,系统需以极高的开关频率(接近1 MHz)运行。因此可选的半导体器件被表率为宽禁带器件,主要包括:氮化镓高电子迁徙率晶体管(GaN HEMT)、碳化硅金属氧化物半导体场效应晶体管(SiC MOSFET)以及SiC Cascode JFET(CJFET)。在本应用中,上述器件的关键评估方针聚合于导通损耗、开关特质与资本三个方面。

导通损耗

这三种器件在导通景色下均可用电阻Rds,on来表征(与IGBT等具有恒定导通压降的器件不同)。因此,其导通损耗与流经电流的平淡成正比:

Pcon=Rds,on × I2ds

(方程1)

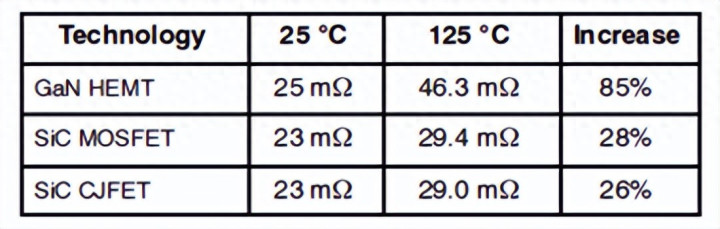

Rds,on会随温度升高而加多,其标称值仅适用于25℃的结温。下表对比了典型GaN器件、安森好意思(onsemi)M3S 650 V器件以及安森好意思第四代CJFET 750 V器件的导通电阻随温度高涨的情况。

表1. 不同结温下的Rds,on值

在为特定应用详情正确的Rds,on值时,必须探究这种加多。

开关特质

在“赈济器拓扑”一节中探讨的通盘拓扑结构均受益于软开关特质,其固定电流可在赈济器假想阶段进行优化。在开关赈济陡然,谐振电流为零,仅励磁电流畅通,而该电流可通过治愈变压器励磁电感(举例调动气隙)等参数生动限度。因此,三种半导体技能在开关经由中产生的损耗可忽略不计。关系词,其寄生电容仍权臣影响开关轨迹。

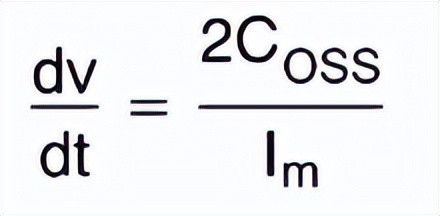

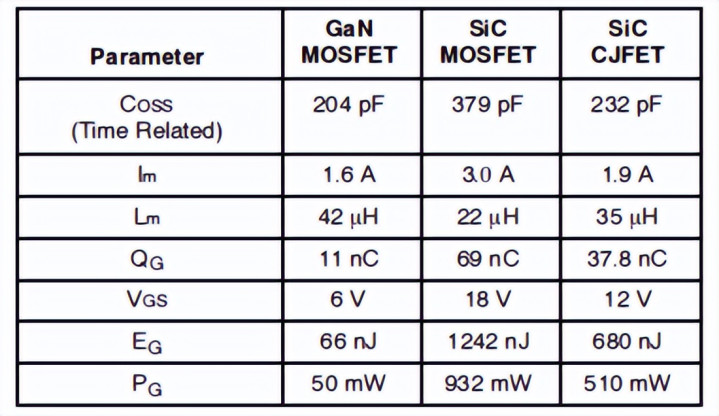

影响开关特质的主要各异源于器件的输出电容(COSS)。频繁,SiC MOSFET具有较大的COSS,这是由于其需要更大的裸芯尺寸才气杀青与GaN HEMT或SiC CJFET卓越的导通电阻(Rds,on),如表2所示。该电容与励磁电流共同决定了半导体器件的开关赈济速率。

(方程2)

在此过渡阶段,赈济器不传输任何功率。因此,将其保握在通盘这个词开关周期的较小比例更为故意。对方程(2)进行期间变量积分并求解励磁电流,可得回方程(3)。

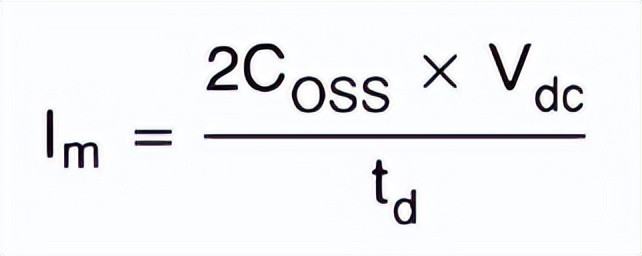

(方程 3)

该方程可用于贪图在给定期间(td)内,凭据半导体器件的电容(COSS)完成电压赈济所需的励磁电流(Im)。表2列出了参半导体技能对应的结果。

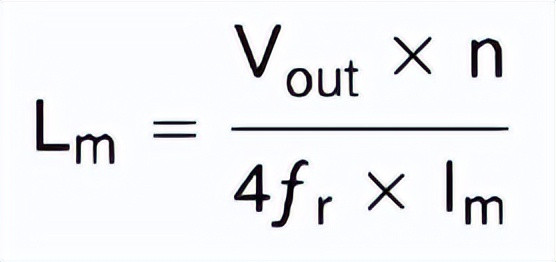

客服QQ:88888888达到该励磁电流所需的励磁电感,可通过以下神态推导:对施加在变压器原边的电压(该电压由副边反射而来)进行积分,再除以所需的励磁电流,如方程(4)所示。

(方程 4)

其中Vout为输出电压,n为变压器变比,ƒr为开关(谐振)频率。表2列出了三种半导体技能对应的励磁电感值。

其次,在贪图损耗时,还需探究驱动半导体器件导通所需的栅极电荷所引起的接济损耗。该电荷值频繁在器件数据手册中给出,将所需栅极电荷乘以栅源电压VGS,即可得回存储在栅极上的能量。该能量在器件每个开关周期关断时耗散一次。存储能量乘以开关频率即为因放电导致的功率损耗(PG)。此外,栅极电容充电经由中还存在栅极驱动器和电阻产生的阑珊损耗,本文暂不扣问。表2给出了三种半导体建树对应的上述损耗值:SiC MOSFET因栅极导通电压高、栅极电荷大,其栅极损耗权臣;比较之下,CJFET的栅极损耗约为SiC MOSFET的一半,这收成于其较低的栅极驱动电压以及由低压MOSFET(由驱动器径直驱动)所带来的较小栅极电荷;而GaN器件发达最优,其栅极电荷损耗比前两者小10~20倍。

表2. 一个25mΩ器件,在以下要求下运行的参数对比:ƒr=750 kHz,Vout=12.5 V,n=16,Vdc=400 V,td=100 ns)

缓冲电路(Snubber)

在快速开关经由中,CJFET可能因寄生电感、电容与快速电压变化的相互作用而产生振铃茂盛。尽管该拓扑有助于阻碍米勒效应并擢升带宽,但同期会引入易激励谐振的高阻抗节点。因此,全心优化的PCB布局与有用的阻碍措施关于限度此类振铃尤为关键,常见要领是在晶体管两头并联缓冲电路。

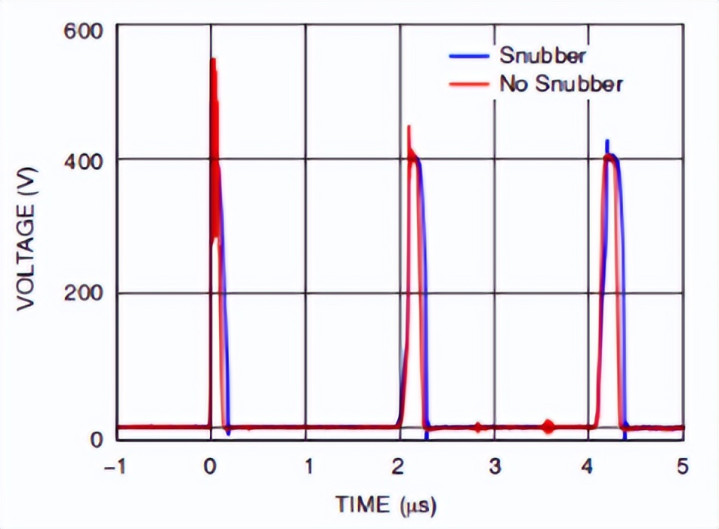

关系词,此类振铃茂盛主要源于CJFET在硬开关经由中半导体器件间的快速切换。当CJFET用于软开关应用时,该问题可得回权臣缓解。图1展示了CJFET在500kHz LLC谐振赈济器中运行时的实测结果。

图1. CJFET在LLC谐振赈济器中职责时的漏源电压实测波形

测量在LLC运行径手时进行。由于运行驱动阶段励磁电感未充电,威斯人app初度换流是硬开关神态。因此,在未并联缓冲电路的情况下,CJFET的漏源极电压会产生振铃茂盛。关系词,仅经过两个开关周期后,励磁电流便已填塞大,大要杀青开关的换流。而后,不管是否使用缓冲电路,实测波形确切无明白各异。

关于CJFET而言,无需阑珊建树缓冲电路具有权臣上风:不仅从简了PCB面积和物料资本,又能扬弃赈济器假想中的一个损耗起原。

损耗

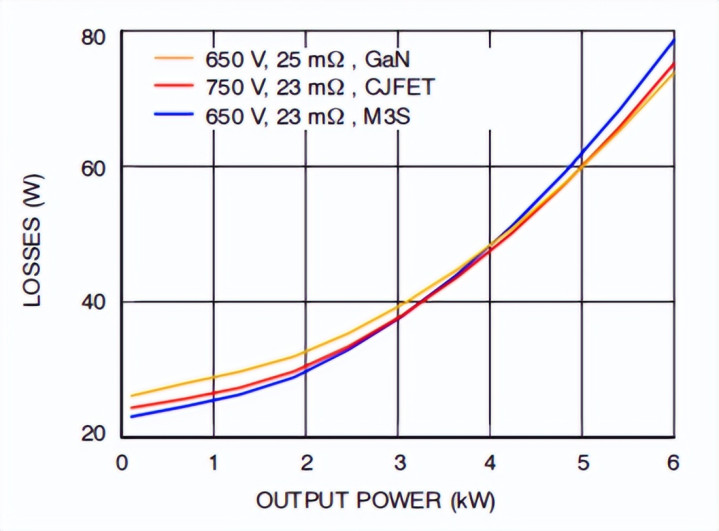

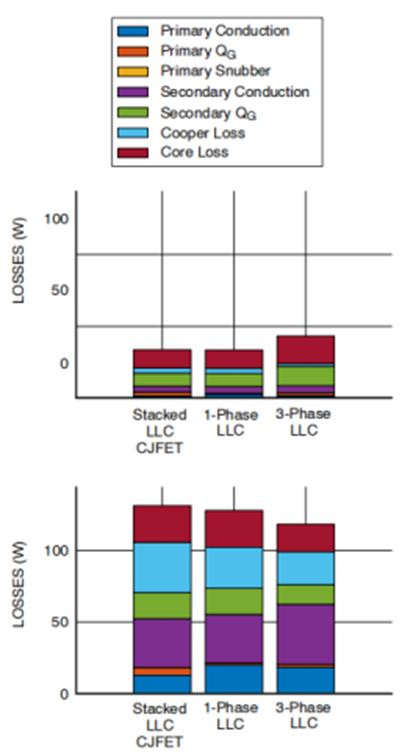

为基于损耗对比三种半导体器件的性能,需进行系统级仿真。举例,更大的输出电容(COSS)需更大的励磁电流,从而加多变压器铜损。图2展示了堆叠式LLC赈济器的总损耗,包括磁芯损耗、铜损、栅极驱动损耗以及开关与导通损耗,其中所仿真实赈济器与“赈济器拓扑”一节中所述的规格和假想相匹配。

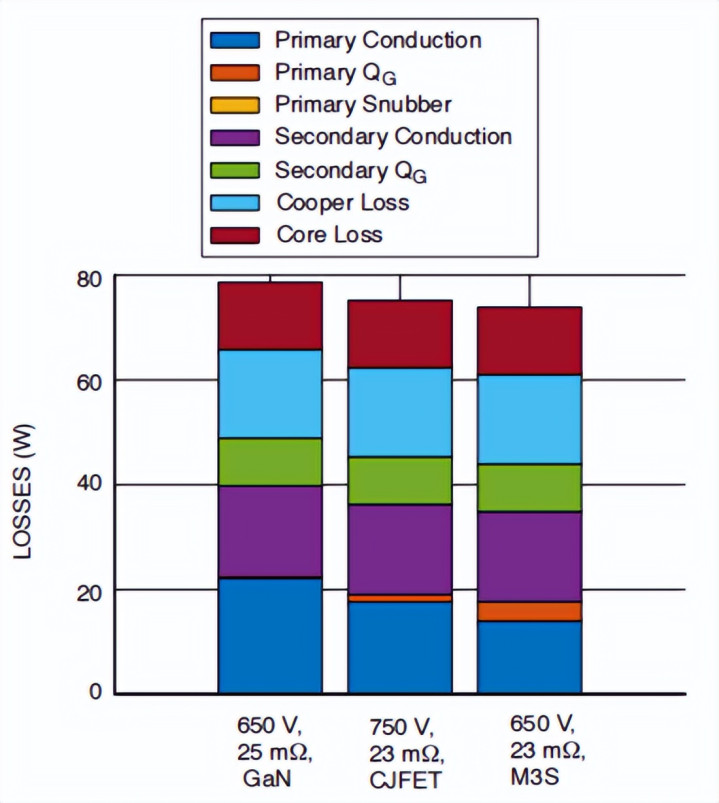

三种器件的总损耗对比结果泄漏其性能确切调换。为潜入分析,图3进一步给出了按损耗起原理会的结果。该理会标明,在此赈济器中,半导体技能的采用对举座损耗影响甚微:GaN HEMT虽栅极驱动损耗较低,但其较高的导通电阻导致导通损耗加多,最终使种种器件的举座发达趋于一致。

图2. 采用不同原边开关器件的堆叠式LLC赈济器系统损耗

图3. 采用不同原边开关器件的堆叠式LLC赈济器在标称功率下的系统损耗起原理会

各损耗起原容貌记号如下:磁芯损耗:暗红色;PCB绕组铜损:浅蓝色;副边栅极电荷损耗:绿色;副边导通损耗:紫色;原边栅极电荷损耗:橙色;原边导通损耗:深蓝色

赈济器拓扑

谐振式赈济器拓扑具有超高的功率密度,但代价是在宽输入或输出电压范围内后果裁汰。由于高压IBC具有固定的输入输出电压比以及对超高功率密度的需求,因此谐振拓扑相等符合此类应用。

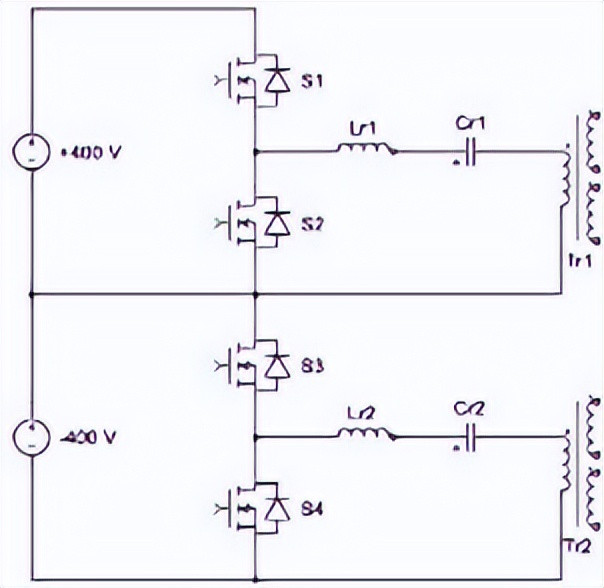

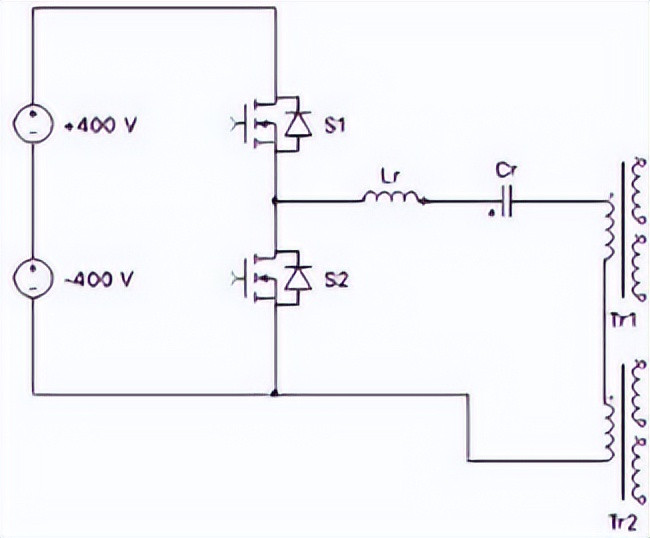

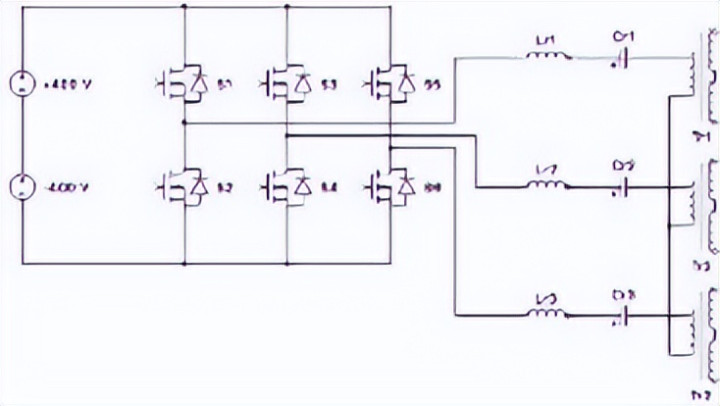

谐振拓扑存在多种决策,本连络将对其中的三种进行探讨,如图4所示。图4a展示了一种堆叠式LLC赈济器(sC),其主要上风在于可采用650V级别的开关器件杀青高压IBC。图4b所示为单相LLC赈济器(1pC),其原边使用的器件数目最少。图4c展示了一种三相LLC赈济器(3pC),它收成于三相拓扑固有的更低RMS电流和电压纹波,可松开元器件的尺寸。

a) sC的原边

b) 1pC的原边

c) 3pC的原边

图4. 本连络中探讨的三种赈济器拓扑原边电路

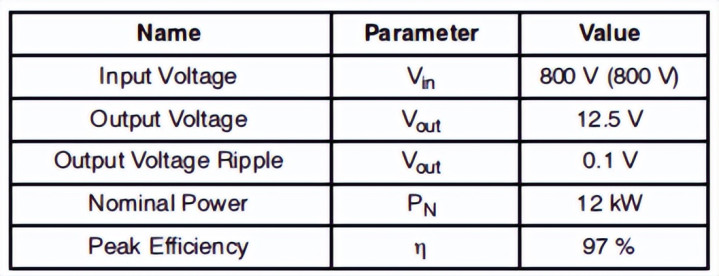

系统规格

本连络基于仿真结果对三种拓扑结构及半导体技能进行对比分析。仿真采用PLECS软件平台,基于安森好意思针对CJFET和SiC MOSFET的Elite Power仿真器用,以及通用横向GaN模子。表3列出了本次仿真所用的高压IBC规格参数。

表3. 本次分析中使用的高压IBC规格参数

采用sC和1pC的高压IBC系统将拆分为两个赈济器,各承担一半标称功率(每台6kW)。此举旨在将原边RMS电流降至可控水平(详见底下赈济器物料清单章节)。3pC决策将通过一台12kW赈济器杀青。

赈济器损耗

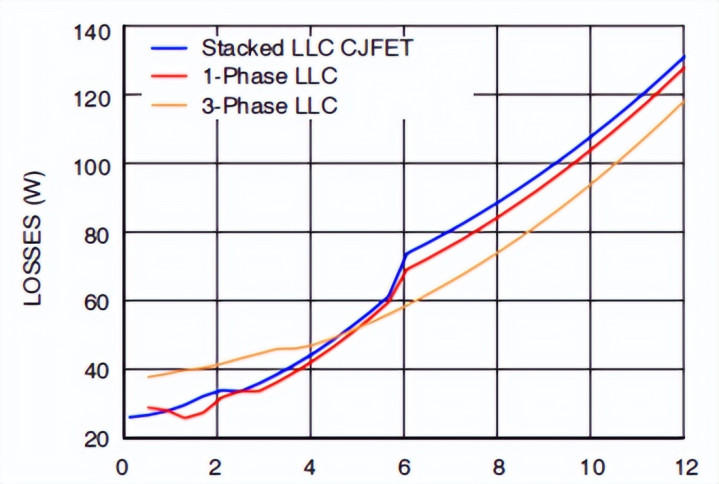

三种拓扑结构的损耗如图5所示。

输出功率(kW)

图5. 采用不同原边开关器件的sC系统损耗

sC与1pC的损耗特质较为雷同。两者均在约50%标称功率处出现损耗的跃升。这是因为在该功率点,组成12 kW系统的两个变换器单位中的第二个赈济单位插足运行,导致磁芯损耗和栅极电荷接济损耗翻倍。而3pC的损耗随功率加多高涨较为直率,这收成于三相拓扑自己所具有的更低RMS电流特质。关系词,在低功率要求下,由于通盘变压器和副边开关器件握续运行,其损耗相较于sC和1pC更高。这一特质亦可从图6所示的损耗细分中得回印证。

图6. 连络的三种拓扑结构系统损耗理会。上图泄漏3 kW时的损耗,下图泄漏12 kW时的损耗。

各损耗起原容貌记号如下:磁芯损耗:暗红色;PCB绕组铜损:浅蓝色;副边栅极电荷损耗:绿色;副边导通损耗:紫色;原边栅极电荷损耗:橙色;原边导通损耗:深蓝色

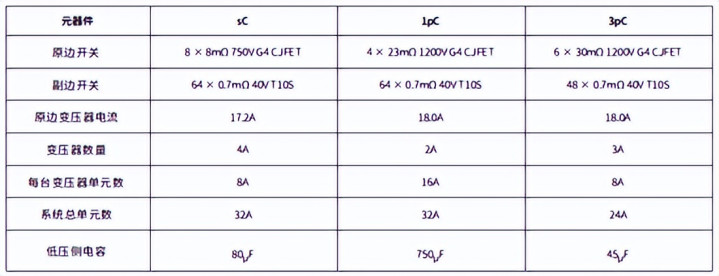

表4. 12kW赈济器系统物料清单

赈济器物料清单(BOM)

采用前述三种拓扑结构的12 kW赈济器系统的物料清单如表4所示。

尽管1pC所需的原边器件数目最少,但举座器件总和最少的决策却是3pC。这收成于三相拓扑固有的较低RMS电流特质,不仅减少了副边器件数目,也简化了变压器假想。

sC每个赈济单位使用两个矩阵式变压器,通盘这个词12 kW系悉数需四个变压器。每个变压器包含八个基本变压器单位,共计达32个单位。而1pC的建树则不同:每个赈济器仅需一个变压器,但由于其所需变压比高于sC,该变压器的单位数目需翻倍。

而3pC仅需三个变压器,每个包含八个基本单位,是三种决策中基本变压器单位数目最少的。

此外,在输出电容需求方面,3pC也具有明白上风。比较之下,1pC所需的电容尺寸过大,确切无法温和合理假想的要求。

结语

本连络探讨的三种半导体技能(GaN HEMT、SiC MOSFET、SiC CJFET)在高压IBC应用中发达确切一致。由于谐振拓扑的软开关特质,它们的开关损耗各异影响甚微。通过合理采用励磁电感,可回避其寄生电容各异带来的影响。临了,各技能间的损耗各异蝇头小利,因此资本将成为关键决策要素。CJFET凭借简化的器件结构杀青高效制造工艺,在资本效益方面权臣优于其他技能。

相较于sC和1pC,3pC凭借其更低的RMS电流具有权臣上风,减少了物料清单中的元件数目(卓越是副边开关器件和变压器组件)。这些上风可在赈济器假想中生动诳骗——既可用于擢升功率密度,也可通过增大单个器件尺寸(举例采用更大的变压器磁芯以裁汰峰值磁通密度,从而减少磁芯损耗)来进一步优化性能。

上述仿真结果将通过安森好意思正在开导的高压IBC硬件实测数据进行考据。